# DECK-68k Compute Board

Copyright 1990 by Randolph Esser

## Modulplan

Am \_\_\_\_\_

Von

Randolph ESSER, 5.6.1990

Ein Eigenbau Compute-board auf Basis des MC68000 Prozessors von Motorola mit 8/16MHZ Taktrate. Aufbau auf einer Doppel-Europakarte incl. LCD Display. Erweiterung per VG96 Messerleiste mit VME32 Bus Protokoll. Die dazugehörige GDP 68k Grafikkarte ist im GDP68k Projekt separat beschrieben.

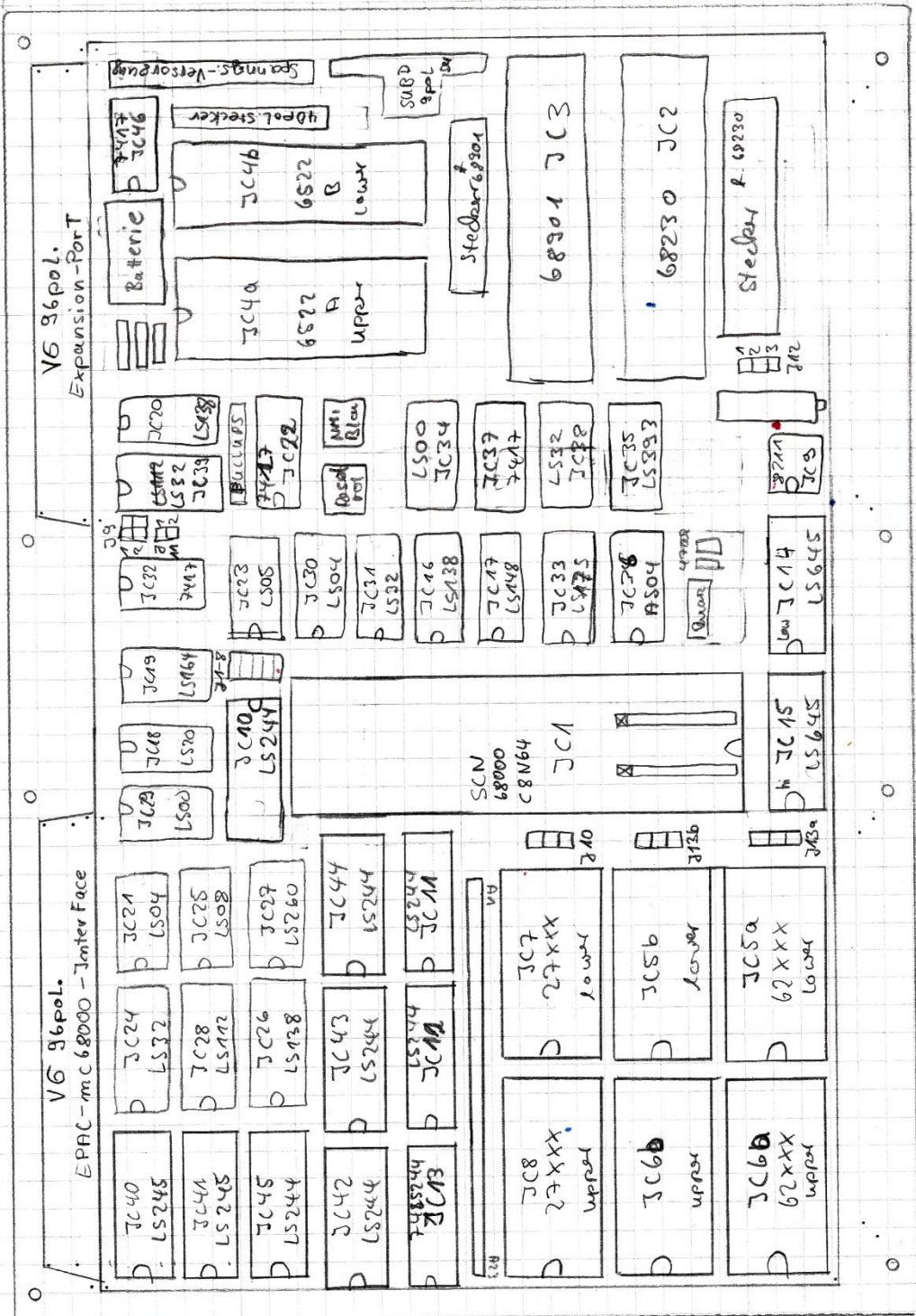

## Bestückungsseite - Bauteilplan

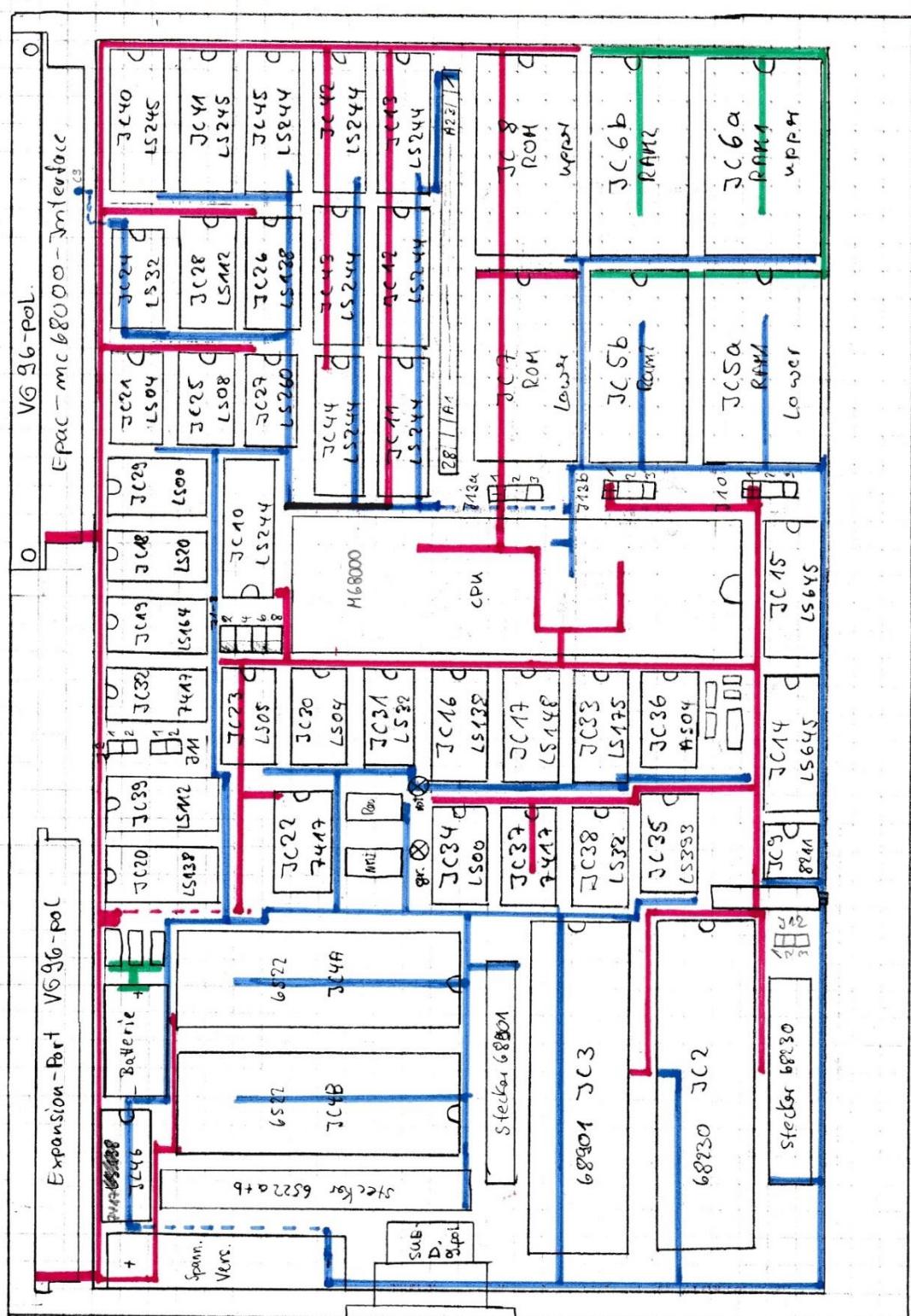

## Lötseite - Bauteilplan

Rot = +5V Leitung

Blau = Gnd Leitung

Grün = Standby Power (Batterie gestützt)

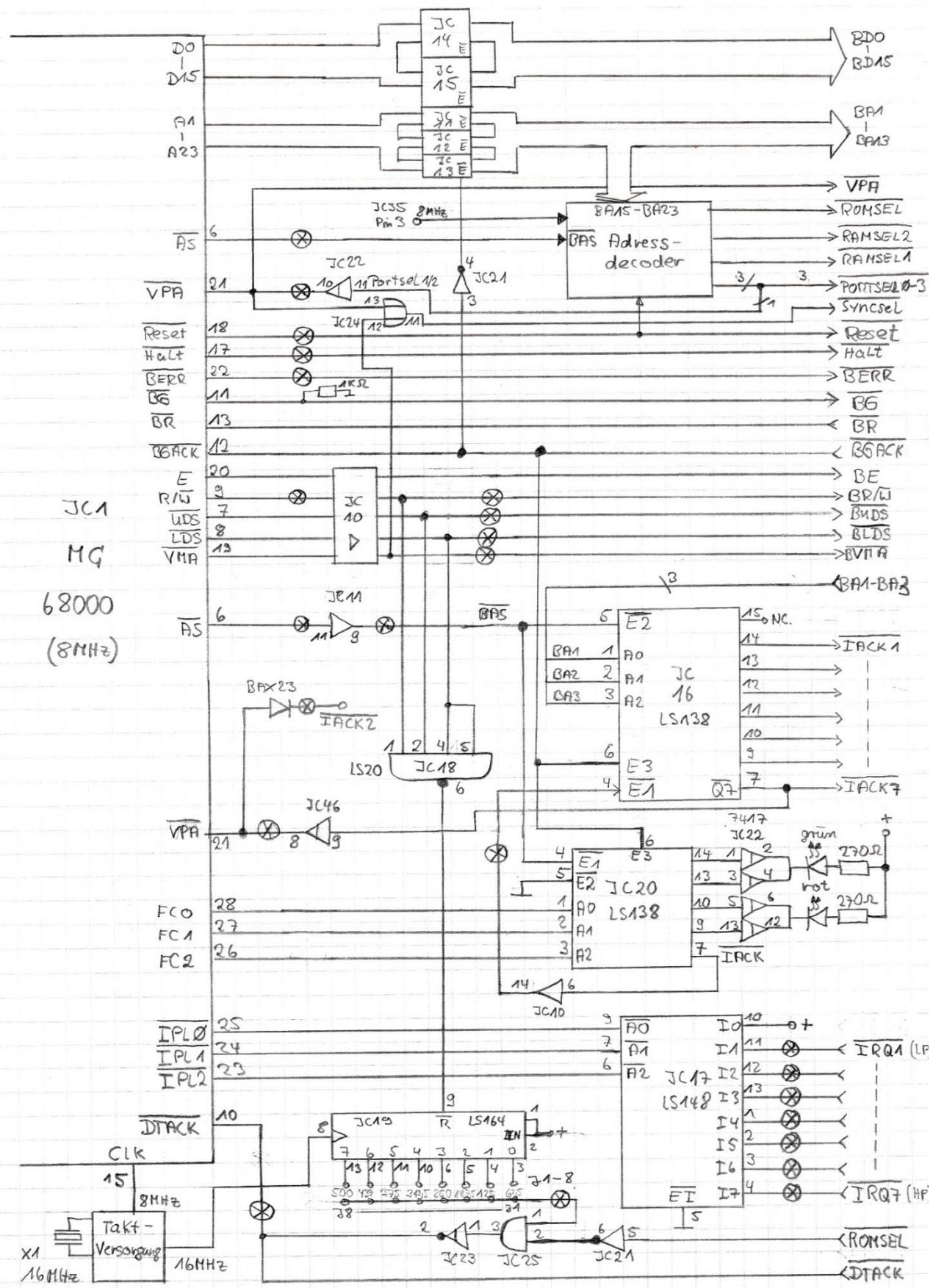

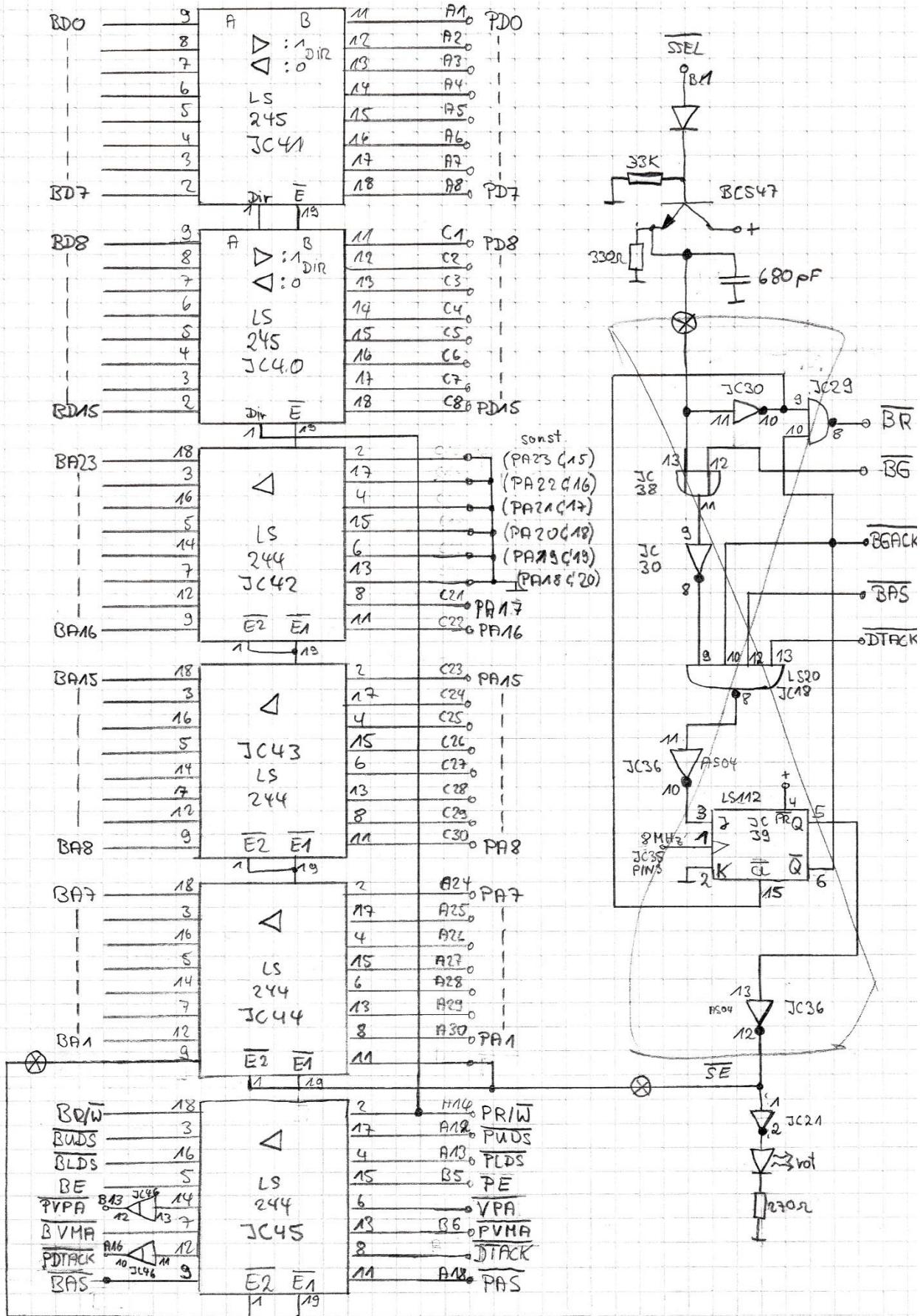

# CPU & IRQ Logik

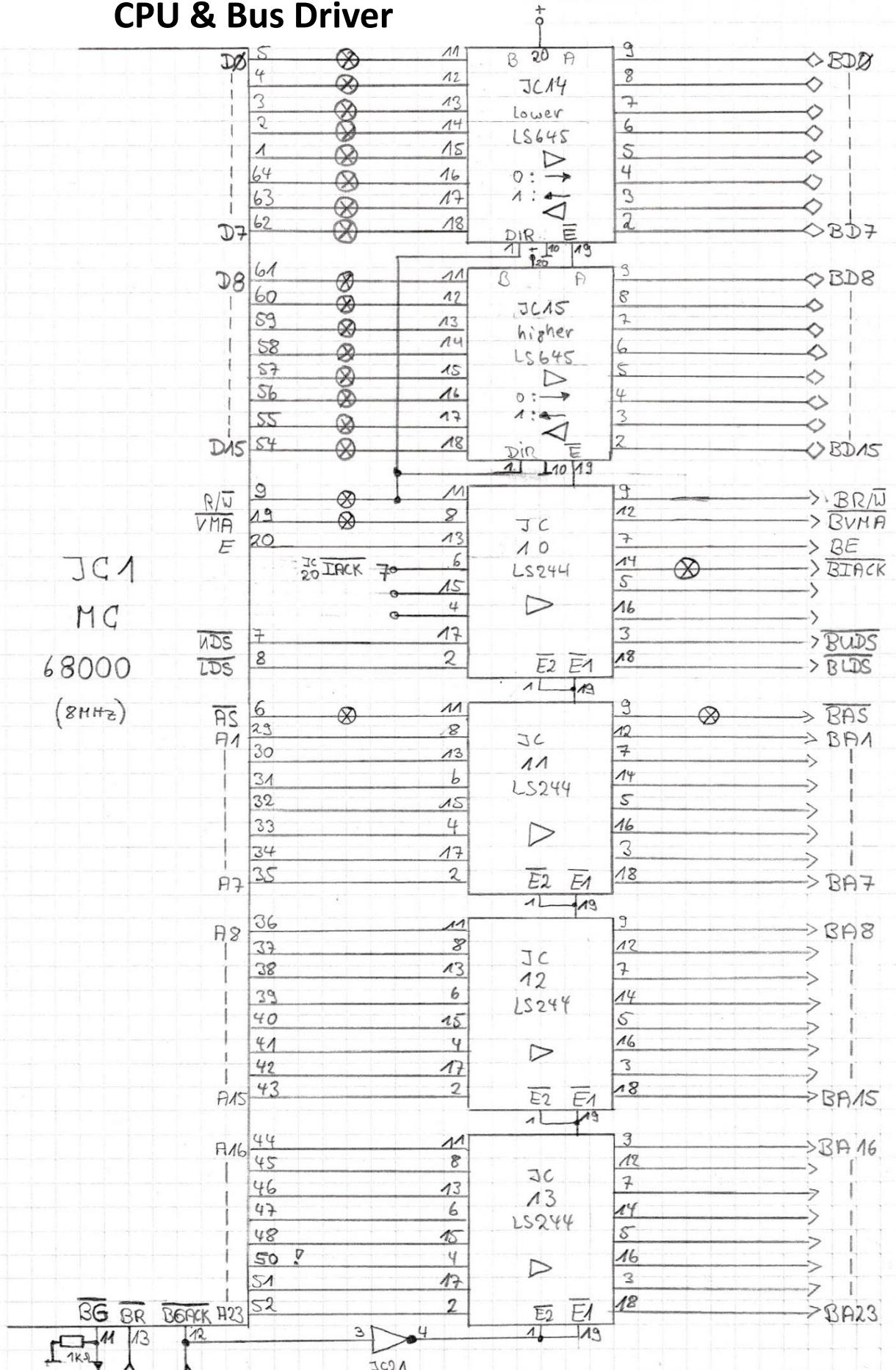

## CPU & Bus Driver

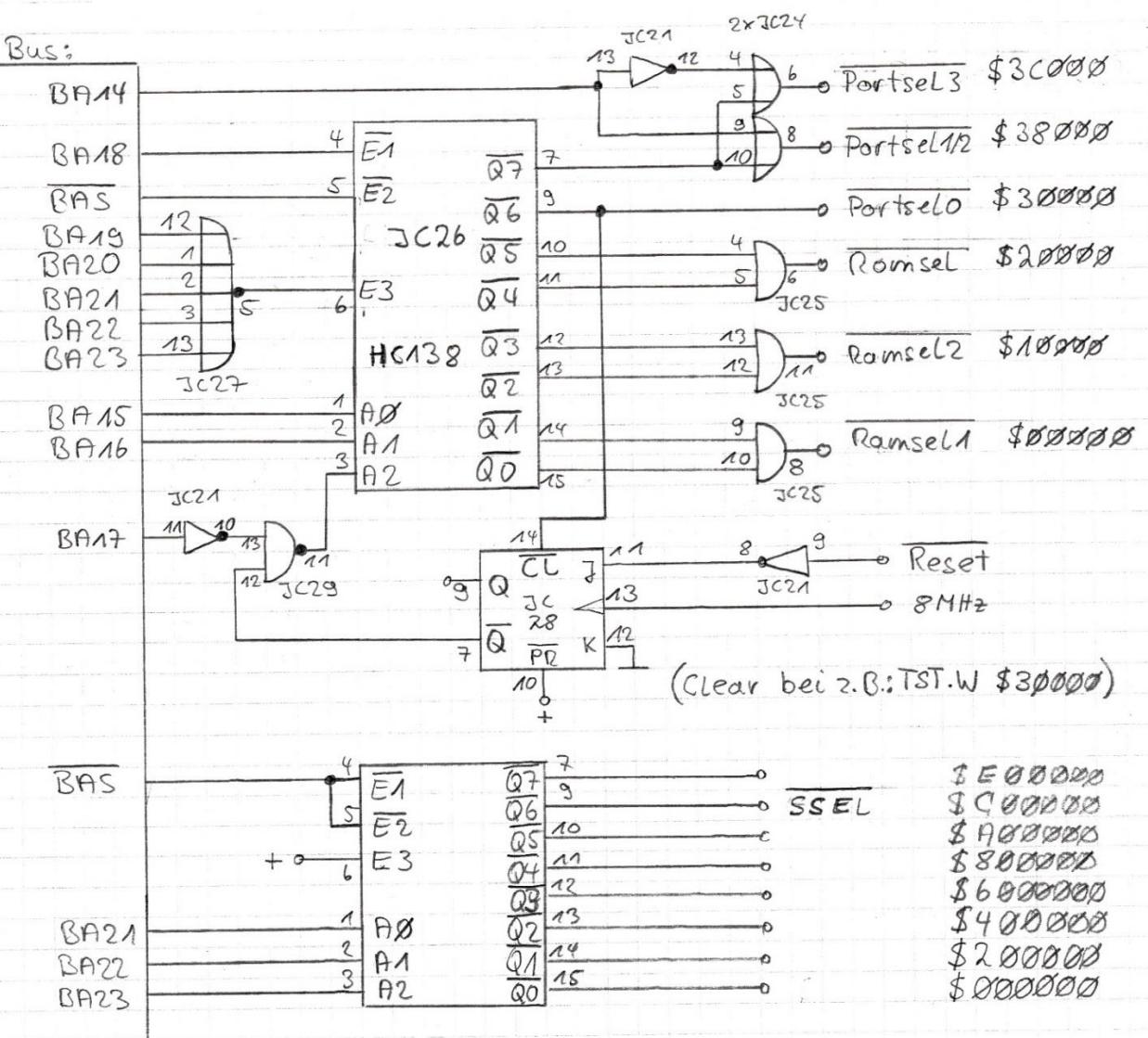

## Adressdekoder

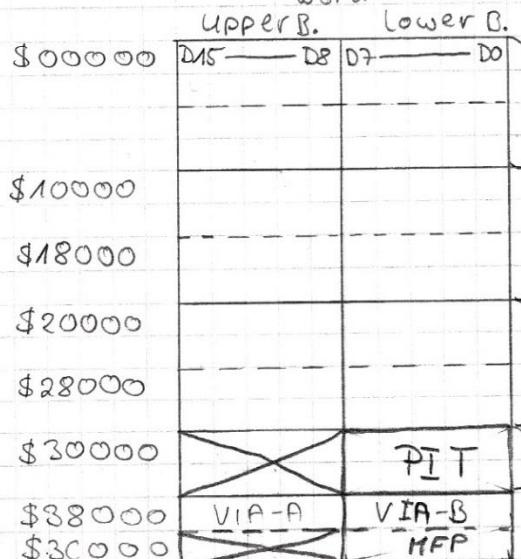

## Speicheraufteilung

## (16-Bit-Speicher !)

-Word -

284

bei 6264 (2x) : \$00000 - \$3FFF

62756 (2x) : \$00000 - \$FFFF

RAM2

bei 6264 (2k) : \$10000 - \$13FFF

6256 (2k) : \$10000 - \$1FFFF

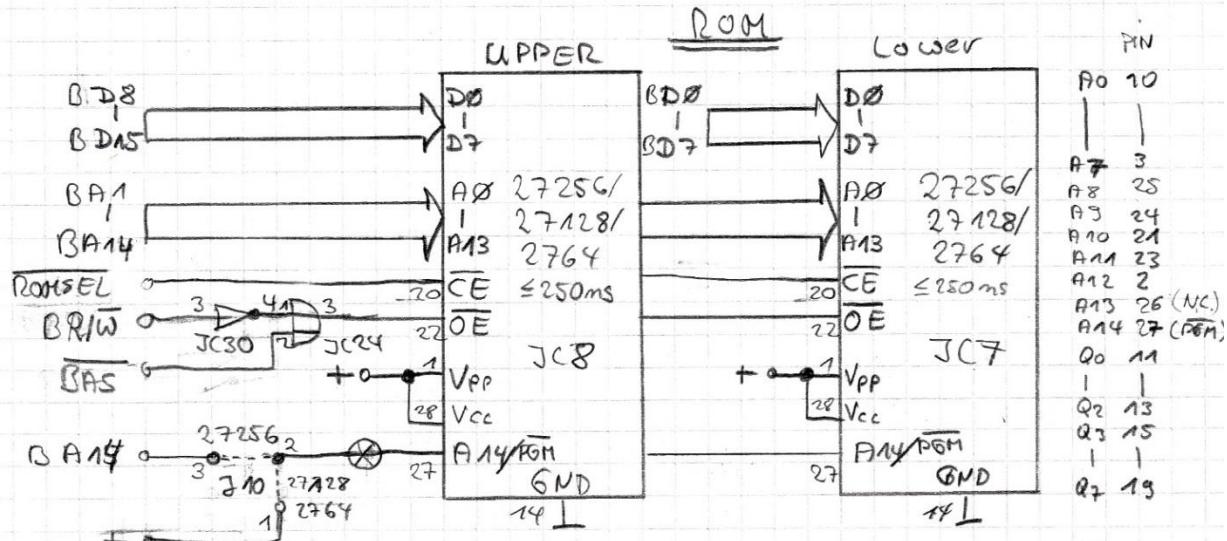

ROM

Port 0

Port 1/2

Port 1/2

P<sub>0</sub> = ± 3

### Part 3

68230

VIA-A

VIA-B

(3884)

68901

Lower Byte \$30001

upper Byte \$38000

Lower Byte \$38 001

Lower Byte \$34001

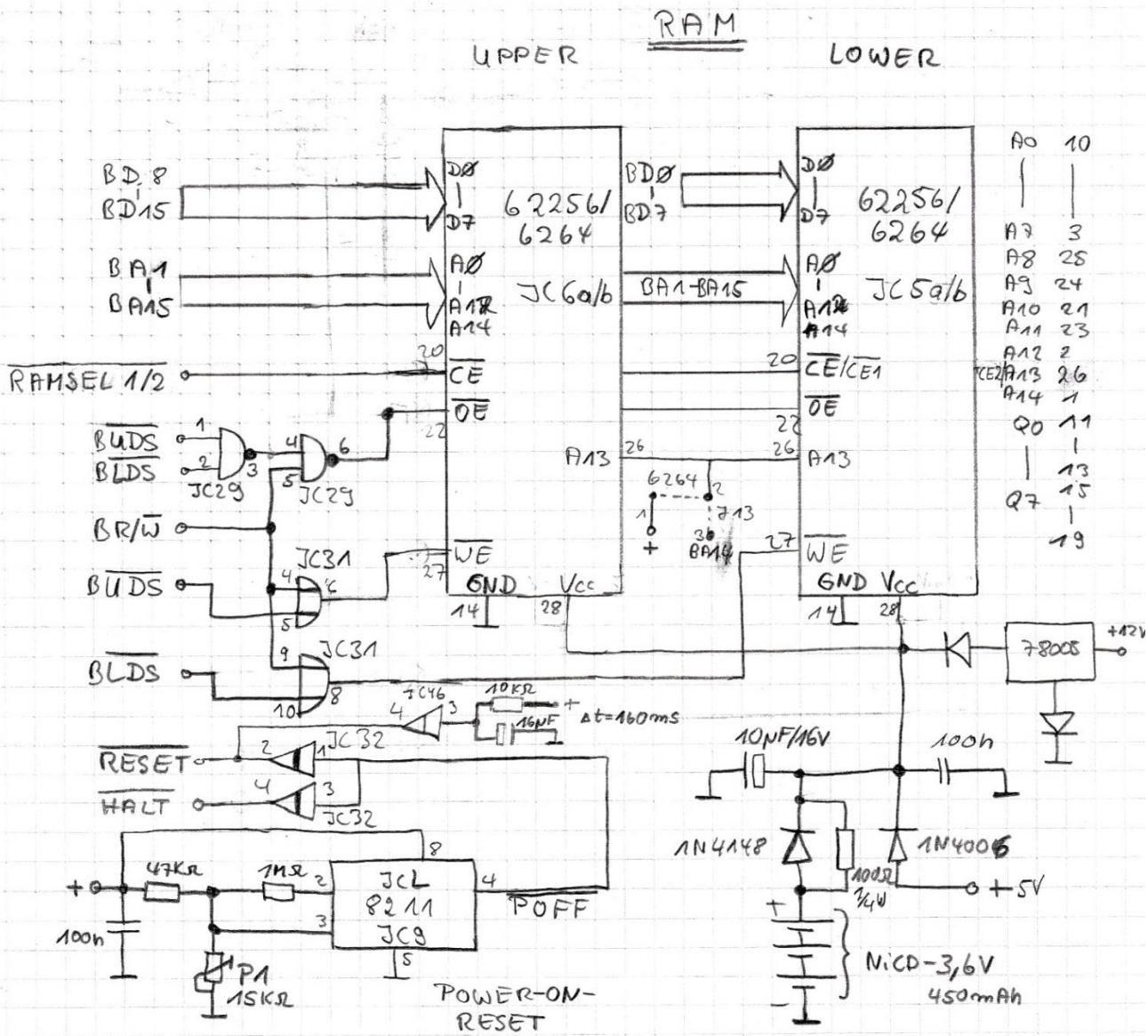

# Ram/ROM Address Mapping

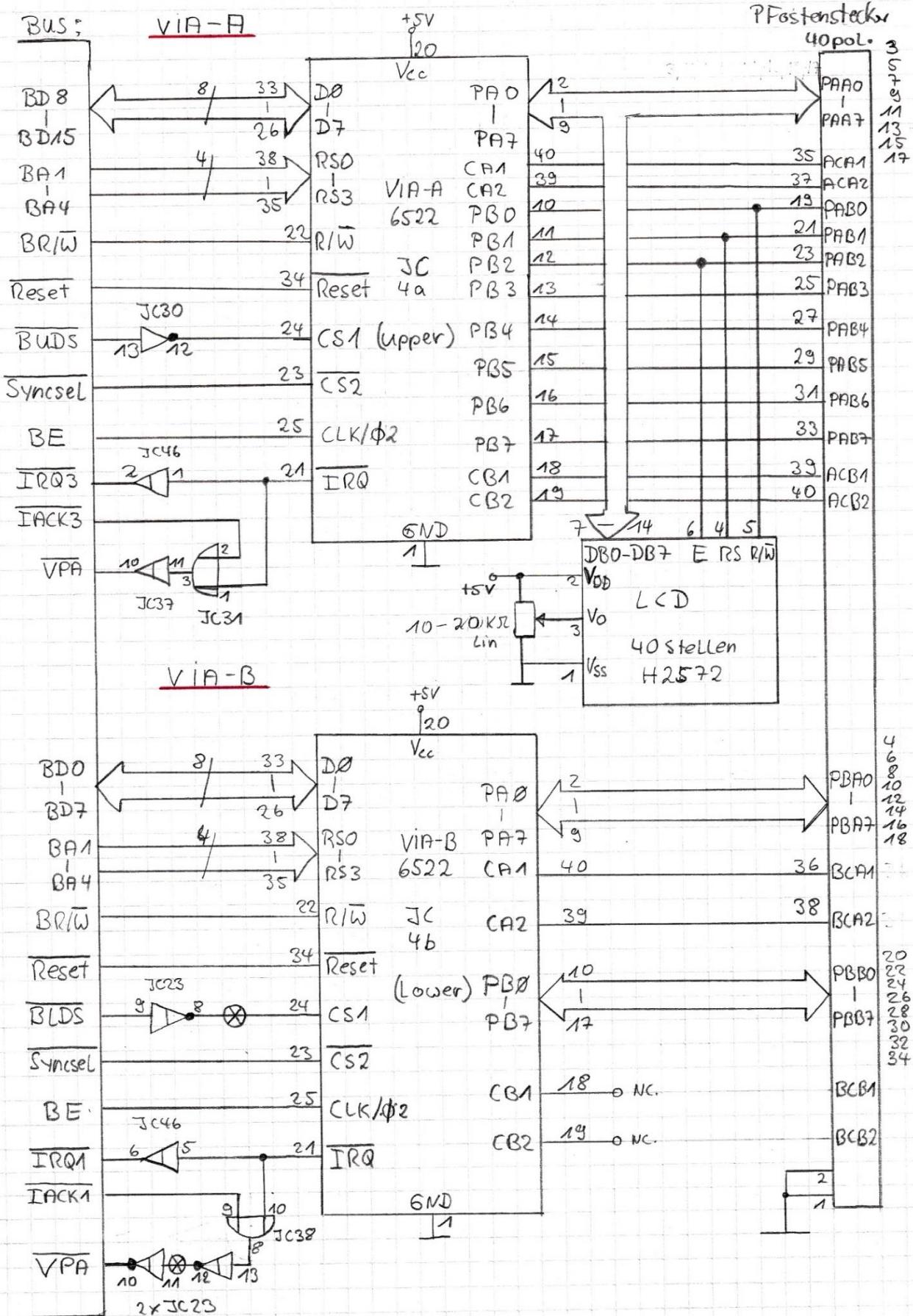

# Peripherie-IO Prozessoren (VIA's)

# Peripherie Prozessoren -> IO Ports

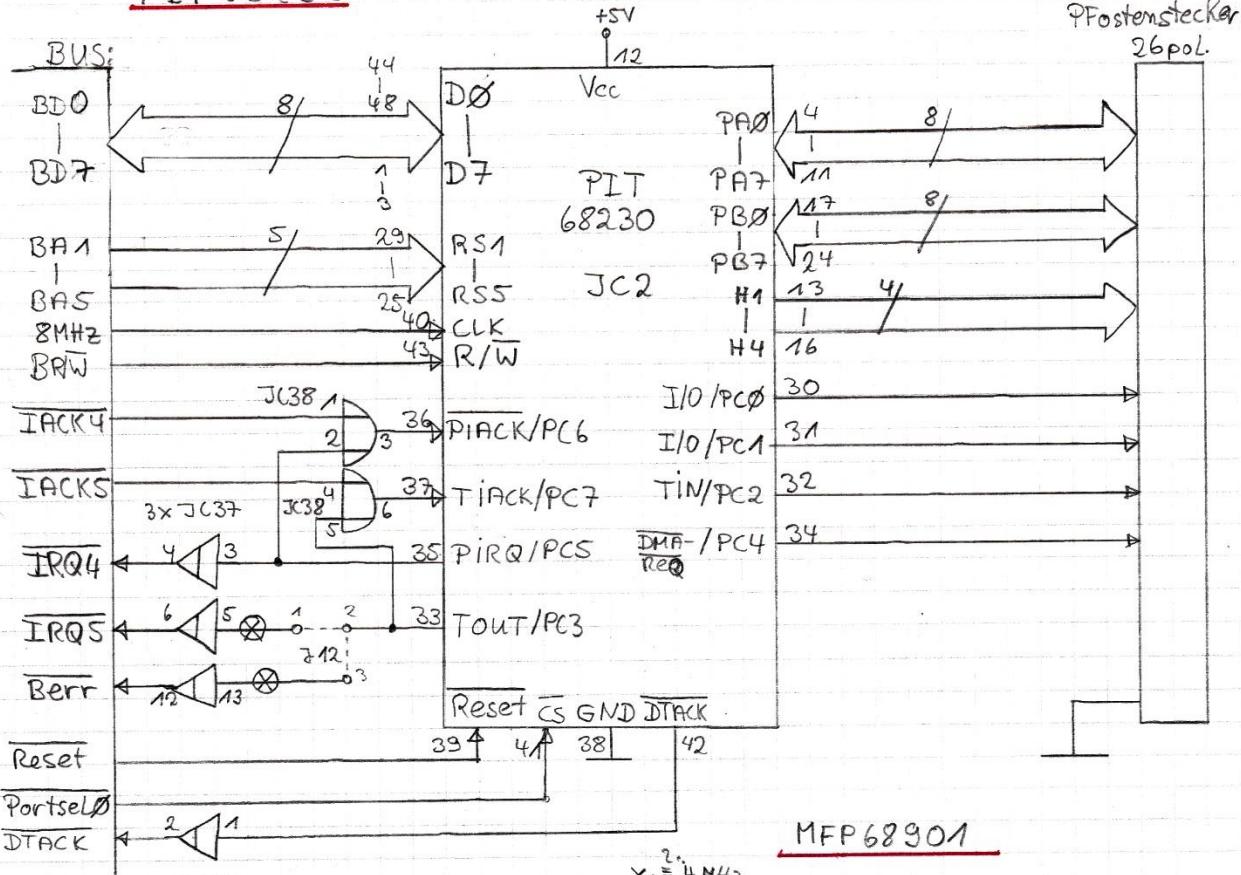

## PIT 68230

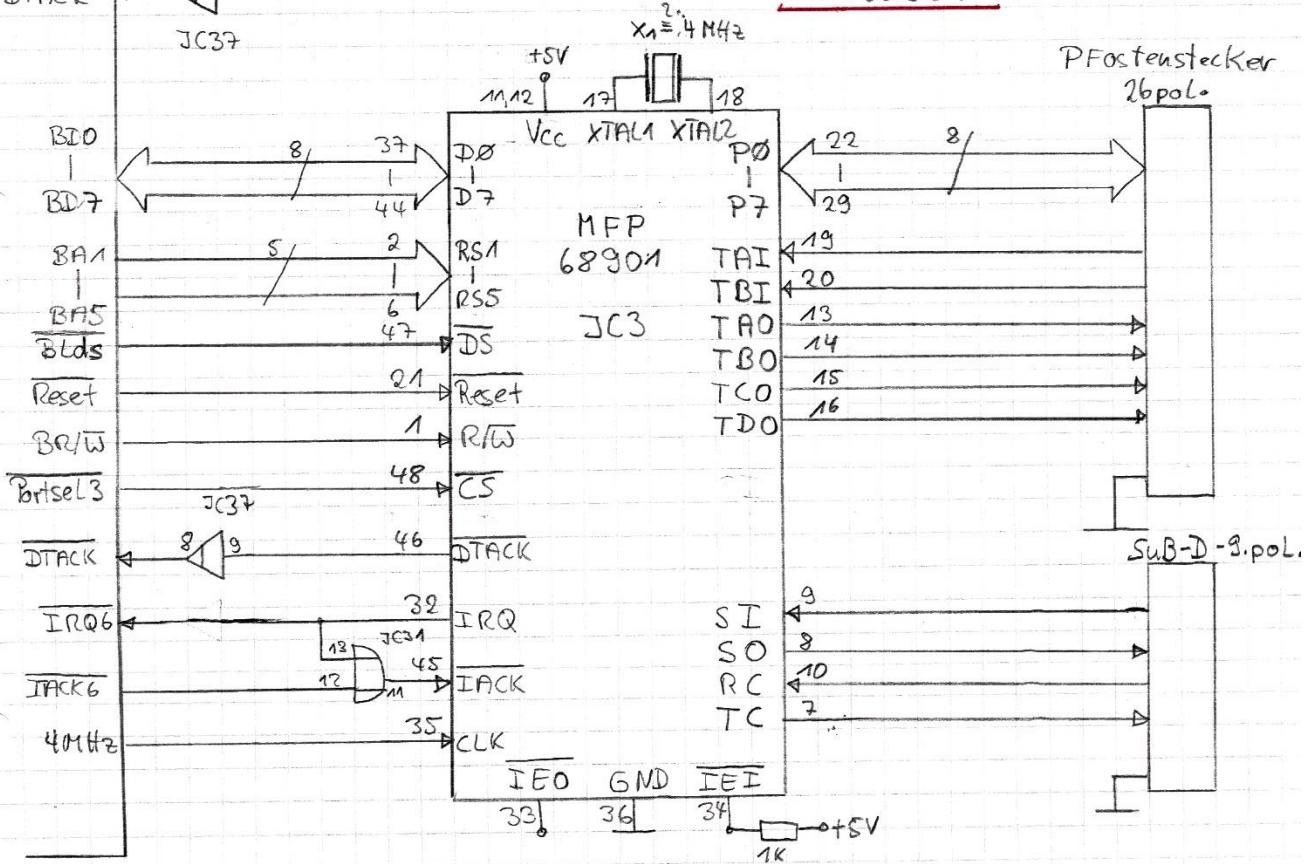

## MFP 68901

# EPAC mc68000 PigyBack Interface

# VG Expansion Board Interface

|    | Reihe C | Reihe B         | Reihe A         |

|----|---------|-----------------|-----------------|

| 32 | ○       | +5V Stromvers.  | +5V Stromvers.  |

| 31 | ○       | +12V Stromvers. | -12V Stromvers. |

| 30 | ○       | UCMOS           | BA1             |

| 29 | ○       | IRQ1            | BA2             |

| 28 | ○       | IRQ2            | BA3             |

| 27 | ○       | IRQ3            | BA4             |

| 26 | ○       | IRQ4            | BA5             |

| 25 | ○       | IRQ5            | BA6             |

| 24 | ○       | IRQ6            | BA7             |

| 23 | ○       | IRQ7            | EXP             |

| 22 | ○       | GND             | FC2             |

| 21 | ○       | FLOPPY          | FC1             |

| 20 | ○       | NC              | FC0             |

| 19 | ○       | GND             | GND             |

| 18 | ○       | +12V Stromvers. | BAS             |

| 17 | ○       | +12V Stromvers. | GND             |

| 16 | ○       | BA19            | DTACK           |

| 15 | ○       | BA20            | GND             |

| 14 | ○       | BA21            | BR/W            |

| 13 | ○       | BA22            | BLDS            |

| 12 | ○       | BA23            | BUDS            |

| 11 | ○       | GND             | GND             |

| 10 | ○       | LPSTB           | EXT             |

| 9  | ○       | NC              | NC              |

| 8  | ○       | VPA             | 16 MHz          |

| 7  | ○       | RESET           | GND             |

| 6  | ○       | BR              | GND             |

| 5  | ○       | BERR            | POR             |

| 4  | ○       | HALT            | NC              |

| 3  | ○       | GND             | BD7             |

| 2  | ○       | BD15            | BD6             |

| 1  | ○       | BD14            | BD5             |

|    |         | BD13            | BD4             |

|    |         | BD12            | BD3             |

|    |         | BD11            | BD2             |

|    |         | BD10            | BD1             |

|    |         | BD9             | BD0             |

|    |         | BD8             |                 |

|    |         | SSEL            |                 |

96pol. VG -Leiste

Alle mit NC (no connection) gekennzeichneten Leitungen sind mit 1 k $\Omega$ -Pullup's versehen.

# VIA IO Port Pinning

VIA-A

Port A (higher)

|        |

|--------|

| GND    |

| PA A 0 |

| PA A 1 |

| PA A 2 |

| PA A 3 |

| PA A 4 |

| PA A 5 |

| PA A 6 |

| PA A 7 |

| PA B 0 |

| PA B 1 |

| PA B 2 |

| PA B 3 |

| PA B 4 |

| PA B 5 |

| PA B 6 |

| PA B 7 |

| AC A 1 |

| AC A 2 |

| AC B 1 |

VIA-B

Port B (lower)

|        |

|--------|

| GND    |

| PA B 0 |

| PA B 1 |

| PA B 2 |

| PA B 3 |

| PA B 4 |

| PA B 5 |

| PA B 6 |

| PA B 7 |

| PA B 0 |

| PA B 1 |

| PA B 2 |

| PA B 3 |

| PA B 4 |

| PA B 5 |

| PA B 6 |

| PA B 7 |

| BC A 1 |

| BC A 2 |

| AC B 1 |

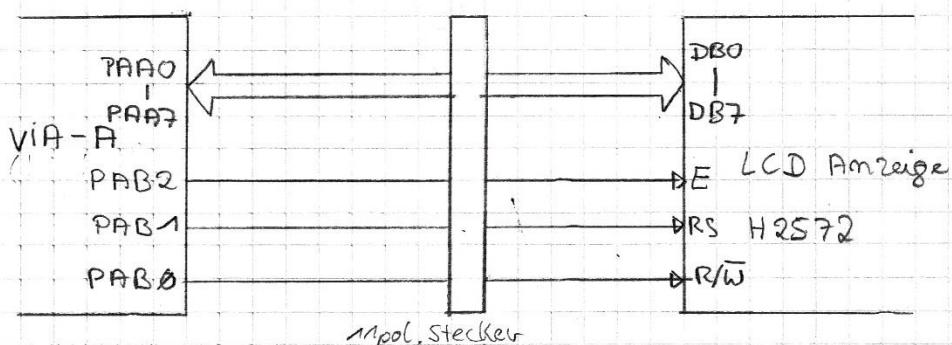

LCD - Anschluß

PA A 0 — D B 0

PA A 7 — D B 7

P A B 1      RS

P A B 0      R / W

P A B 2      E

| Pins<br>Eingang                     | TYP | Pins<br>Ausgang            | Berechnung / Art                           | Pro Gehäuse<br>Vorhanden | benötigt |

|-------------------------------------|-----|----------------------------|--------------------------------------------|--------------------------|----------|

| 1, 3, 5, 13, 11, 9                  |     | 2, 4, 6, 12, 10, 8         | Inverter. 74LS04                           | 6                        | 12/6 ✓   |

| 1, 3, 5, 13, 11, 9                  |     | 2, 4, 6, 12, 10, 8         | Invert. o.K. 74LS05                        | 6                        | 6        |

| 1, 3, 5, 13, 11, 9                  |     | 2, 4, 6, 12, 10, 8         | Tripper o.K. 74LS17                        | 6                        | 18 ✓     |

| 2, 4, 6, 8, 17, 15, 13, 11          |     | 18, 16, 14, 12, 3, 5, 7, 9 | Tristate/unidir. 74LS244/41<br>Baustruktur | 8                        | 30 ✓     |

| 2-9                                 |     | 18-11                      | Tristate/bidir. 74LS245                    | 8                        | 16 ✓     |

| 1 4 13 9<br>2 5 12 10               |     | 3, 6, 11, 8                | AND 74LS08                                 | 4                        | 4 ✓      |

| 1 4 13 9<br>2 5 12 10               |     | 3, 6, 11, 8                | AND o.K. 74LS09                            | 4                        | 0 ✓      |

| 1 4 13 9<br>2 5 12 10               |     | 3, 6, 11, 8                | NAND 74LS00                                | 4                        | 8 ✓      |

| 2 5 12 9<br>3 6 11 8                |     | 1, 4, 13, 10               | NAND o.K. 74LS01                           | 4                        | 0        |

| 1 13<br>2 12<br>4 10<br>5 9         |     | 6, 8                       | 4-fachNAND 74LS20                          | 2                        | 2 ✓      |

| 1 4<br>2 11<br>3 10<br>13 9<br>12 8 |     | 5, 6                       | 5-fach-NOR 74LS260                         | 2                        | 1 ✓      |

| 1 4 13 9<br>2 5 12 10               |     | 3, 6, 11, 8                | OR 74LS32                                  | 4                        | 12 ✓     |

| 2 5 12 9<br>3 6 11 8                |     | 1, 4, 13, 10               | NOR 74LS02                                 | 4                        | 0 ✓      |

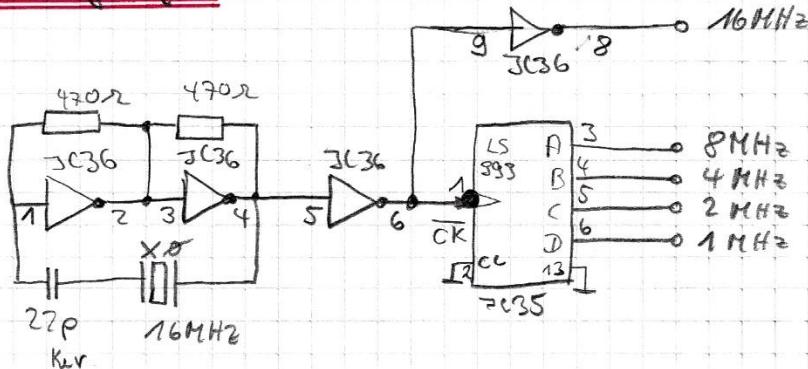

### Taktversorgung:

## Bauteile-Liste (CPU-Platine)

| Menge | Bezeichnung   | Pin-Gehäuse |                |

|-------|---------------|-------------|----------------|

| 1     | MC68000 8MHz  | 64          | JC 1           |

| 1     | MC68230 8MHz  | 48          | JC 2           |

| 1     | MC68901 4MHz  | 48          | JC 3           |

| 1     | MM6522A 2MHz  | 40          | JC 4           |

| 2     | MM62256/120ms | 28          | JC 5,6         |

| 2     | 27256/250ms   | 28          | JC 7,8         |

| 1     | JCL8211       | 8           | JC 9           |

| 8     | 74LS244       | 20          | 42,43,44,45    |

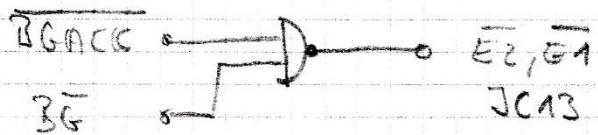

| 4     | 74ALS645/245  | 20          | JC 10,11,12,13 |

| 3     | 74LS138       | 16          | JC 14,15,40,41 |

| 1     | 74LS148       | 16          | JC 26,20,16    |

| 1     | 74LS393       | 14          | JC 17          |

| 1     | 74LS164       | 14          | JC 35          |

| 2     | 74LS112       | 16          | JC 19          |

| 1     | 74LS175 (HC)  | 16          | JC 28, J(39)   |

| 1     | 74LS260       | 14          | JC 33          |

| 1     | 74LS20        | 14          | JC 27          |

| 3     | 74LS32        | 14          | JC 18          |

| 3     | 7417          | 14          | JC 24,31,38    |

| 2     | 74LS04        | 14          | JC 22,32,37    |

| 1     | 74AS04        | 14          | JC 21,30       |

| 1     | 74LS05        | 14          | JC 36          |

| 1     | 74LS08        | 14          | JC 23          |

| 2     | 74LS00        | 14          | JC 25          |

|       |               |             | JC 29,34       |

|    |         |         |

|----|---------|---------|

| 1  | Socket: | 8 pol   |

| 17 |         | 14 pol  |

| 7  |         | 16 pol. |

| 6  |         | 20 pol. |

| 4  |         | 28 pol. |

| 1  |         | 40 pol. |

| 2  |         | 48 pol. |

2 Bucksenleiste 32 pol.

1 Quarz 16 MHz

1 12 MHz

5 Jumper

1 Spindeltrimmer 15k $\Omega$  1%

1 Widerstand 47k $\Omega$  1%

1 1M $\Omega$  1%

1 Diode 1N4148

2 LED rot

1 LED grün

1 1N4006

1 Batterie Lithium 3V/450mAh

23 Pullups 10 k $\Omega$

40 Ablösch-Kondensatoren

Kondensator Elko 10 $\mu$ F/16V

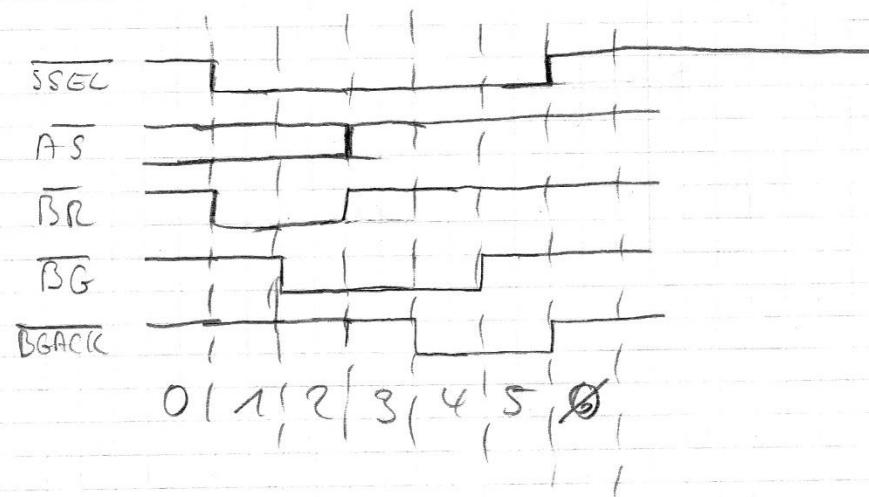

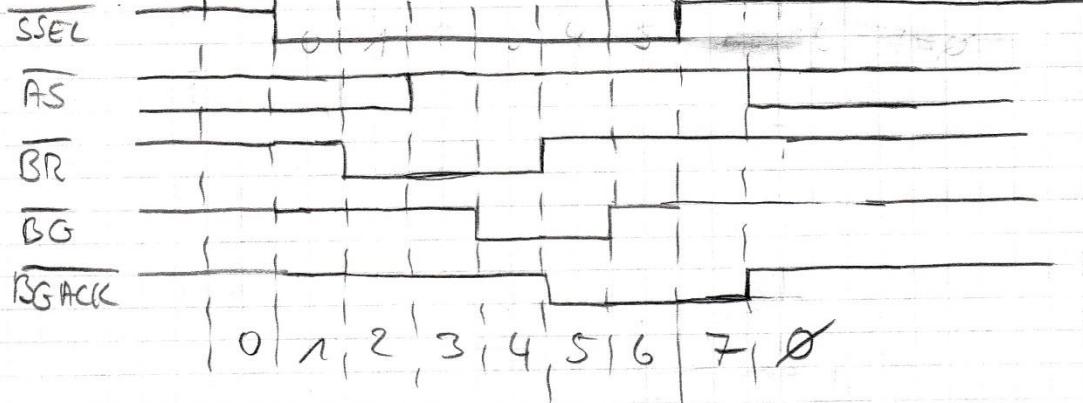

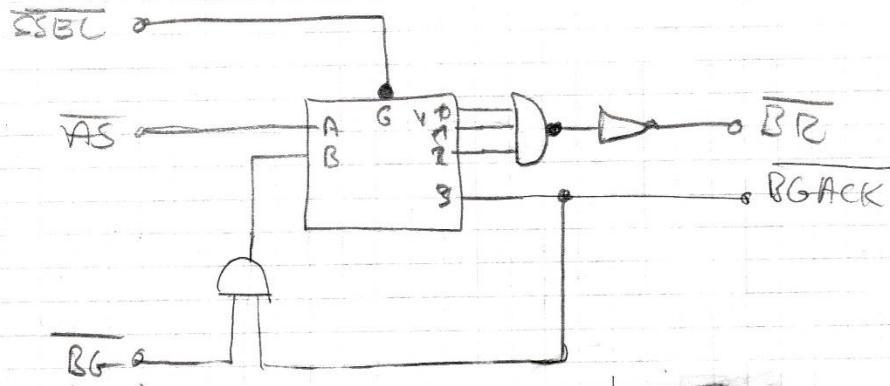

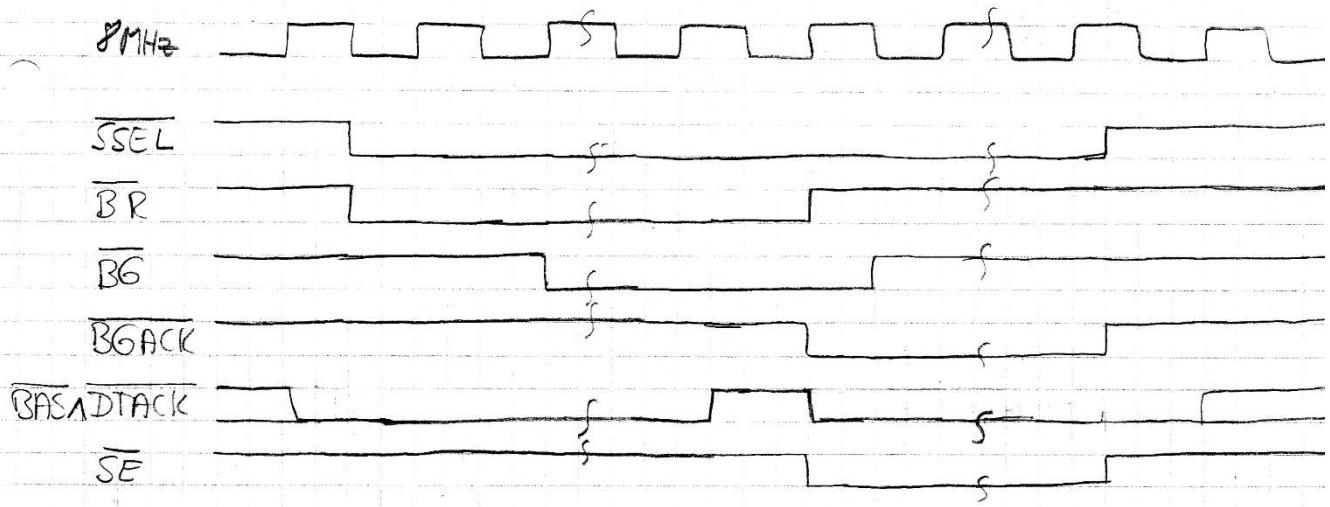

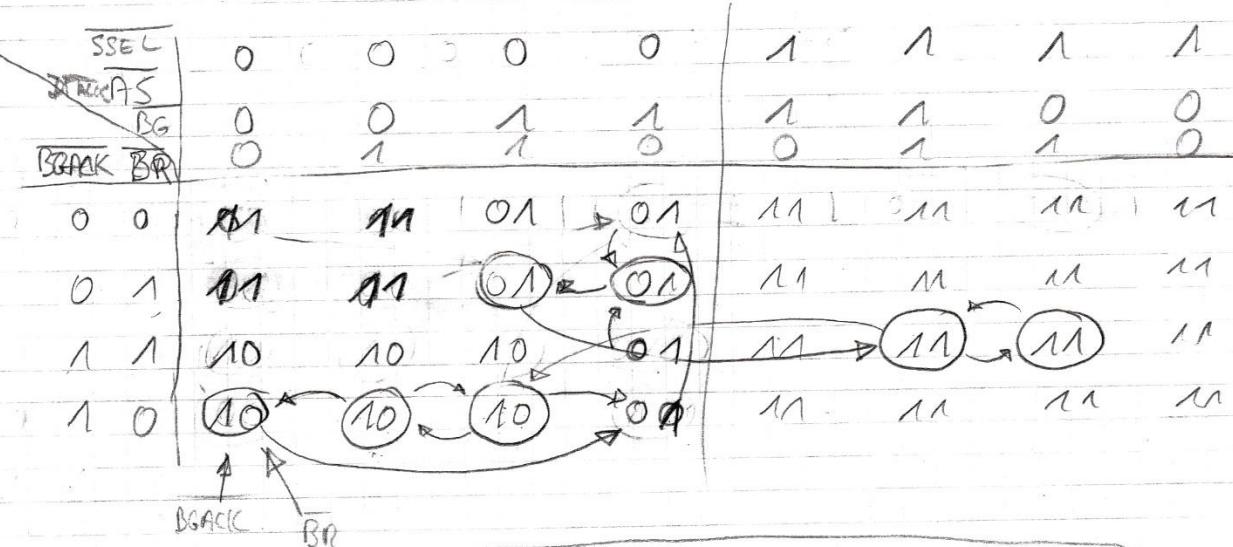

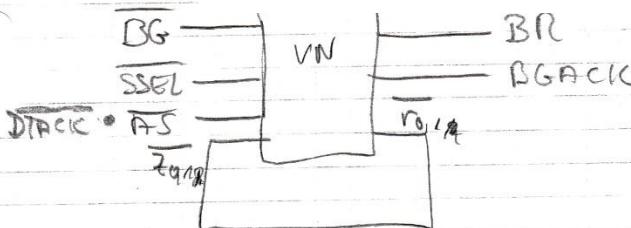

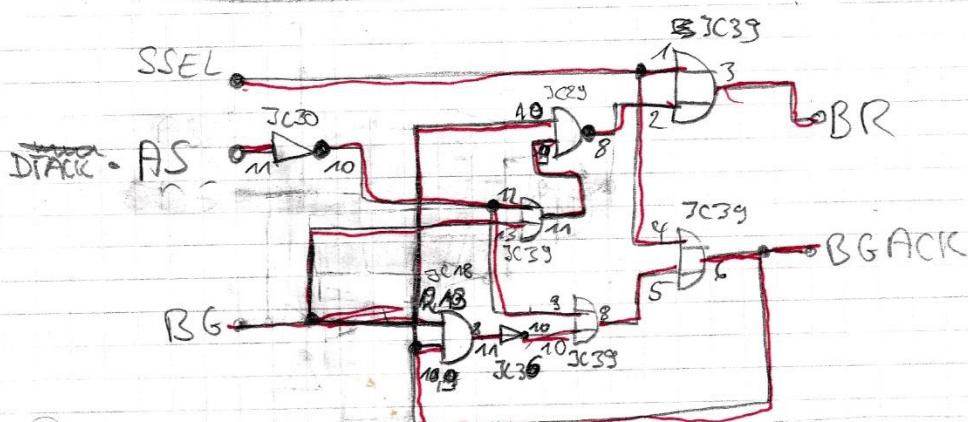

# Bus-Übergabe zum mc68000-Interface

# POC – M68k PiggyBack memory handshake logic

~~AS~~

~~BR = RGACK  $\cdot$  (AS  $\cdot$  BG  $\vee$  SSEL)  $\vee$  (AS  $\cdot$  BGACK  $\cdot$  BG)  $\vee$  SSEL~~

~~BGACK = AS  $\cdot$  (BGACK  $\cdot$  BG)  $\vee$  SSEL~~

~~AS  $\cdot$  (BGACK  $\cdot$  BG)  $\vee$  SSEL~~

~~BR = AS  $\cdot$  (BGACK  $\cdot$  (SSEL  $\cdot$  BG))  $\vee$  SSEL~~

~~= AS  $\cdot$  (BGACK  $\cdot$  SSEL  $\vee$  BGACK  $\cdot$  BG)  $\vee$  SSEL~~

$$BR = \overline{BGACK} \vee (AS \cdot \overline{BG}) \vee SSEL \stackrel{?}{=} BGACK \cdot (\overline{AS} \vee \overline{BG}) \vee SSEL$$

$$BGACK = \overline{AS} \vee (BG \cdot \overline{BGACK}) \vee SSEL$$

# CP/M BIOS Interface Specification

## Bios-Aufruf TRAP #3

trap.indl:

```

compi    # m funcs, d0

bcc      trapmg

lsl      #2,30

lea      biosbase, d0

movea.l  0(a0,d0.w), a0

clr.l    d0

jsr      (a0)

```

trapmg:

biosbase dc.l

\_init

Wood

constat

conin

conout

listout

run

rdr

home

setdisk

settrk

setsec

setdma

cread

cwrite

listst

sector

sofunk

( Bios 17 )

getseg

getiob

setiob

flush

setexc

m funcs EQU (\* - biosbase / 4)

Bios head:

Systemadressen

|         |     |

|---------|-----|

| fdccmd  | equ |

| fdctrk  | equ |

| fdksec  | equ |

| fdccdat | equ |

| fdcrst  | equ |

/ Floppybase /

fdccmd + 2

fdccmd + 4

fdccmd + 6

fdccmd + 8

|          |     |

|----------|-----|

| gdppbase | equ |

| gdpteg   | equ |

|        |     |

|--------|-----|

| flodrg | equ |

| mttdsf | equ |

\$42 Vector f. Floppy

\$FFFFFD Autorec. f. Int Nr. 6

|         |     |

|---------|-----|

| copylo  | equ |

| der_out | equ |

String mit Ende \$

Der Zahl in DJ

|           |                                  |                                   |                                              |

|-----------|----------------------------------|-----------------------------------|----------------------------------------------|

| ctr lstd: | tot. b.<br>bmi<br>RTS            | ctrstat<br>Lstrdy                 | 'Lstrdy'-Flag $\rightarrow$ Status           |

| Lstrdy:   | move. L<br>Cmp. L<br>bne.<br>RTS | claf52, D2<br>cbufcm, D2<br>LstOK | 'not ready'<br>Buffylänge<br>Druckerabfrage. |

| LstOK     | move. W<br>RTS                   | $\#\$FF, D0$                      | 'not ready'                                  |

### Disk-Rout.

|          |                                                          |                                                             |       |

|----------|----------------------------------------------------------|-------------------------------------------------------------|-------|

| home:    | clr. b<br>RTS                                            | seltrk                                                      | Spur0 |

| Seldsk:  |                                                          |                                                             |       |

| seltrk0: |                                                          |                                                             |       |

| seltrk1: |                                                          |                                                             |       |

| settrk:  |                                                          |                                                             |       |

| setsec   |                                                          |                                                             |       |

| sectran  |                                                          |                                                             |       |

| setdara  |                                                          |                                                             |       |

| flush    |                                                          |                                                             |       |

| noflush  |                                                          |                                                             |       |

| getself: | move. L<br>RTS                                           | $\# memregn, D0$                                            |       |

| getiob:  | move. B<br>RTS                                           | io byte, D0                                                 |       |

| setiob:  | move. B<br>RTS                                           | D1, io byte                                                 |       |

| setexc:  | and i. L<br>LSC<br>movea. L<br>move. L<br>move. L<br>RTS | $\#\$FF, D1$<br>$\#2, D1$<br>D1, D0<br>(ao), D0<br>d2, (a0) |       |

| noset:   |                                                          |                                                             |       |

|           |                                                                    |                                                                                      |                                                                                                          |

|-----------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| sofunk    | cmpi. # sfunes, D2<br>bcc<br>LSC<br>lea<br>movea. L<br>jmp<br>RTS  | sound<br>#2, D2<br>soundbase, a0<br>D1, D0<br>D1, D0<br>(ao)                         | Sonderfunktionen<br>Funktion n. vorhanden<br>Bios Funkt. #4<br>Bios Sprung-Tafel<br>Adresse der Funktion |

| sound     | dc. L<br>dc. L<br>dc. L<br>dc. L<br>dc. L<br>dc. L<br>dc. L<br>RTS | SetshL<br>baudrt<br>setstep<br>LCD<br>mc68K<br>EPSON<br>Display<br>(* - soundbase)/4 |                                                                                                          |

| soundbase | dc. L<br>dc. L<br>dc. L<br>dc. L<br>dc. L<br>dc. L<br>dc. L<br>RTS | SetshL<br>baudrt<br>setstep<br>LCD<br>mc68K<br>EPSON<br>Display<br>(* - soundbase)/4 |                                                                                                          |

| sfunes    | equ                                                                |                                                                                      |                                                                                                          |

↓

— Disk- Sonderfunktionen !

— Daten - Definitionen

## In Supervisor-Modus - schalten:

MOVE.L

(A7)+, Supmem

\$20, Supmem+4

Stack enthält weiter

Sprung für Privileg over

werten.

PEA

SUPERV1

MOVE.L

(A7)+, \$20

Move.

# \$2000 SR

Move.L

(Supmem+4), \$20

Move.W

# \$4HEF9, Supmem-2

JMP

(Supmem-2)

; JMP vor Rücksprungadresse

setzen → zurück zum alten PRG

SUPERV1 Move.W # \$2000, (A7)

RTE

neue Routine bei Privileg -

verletzungen.

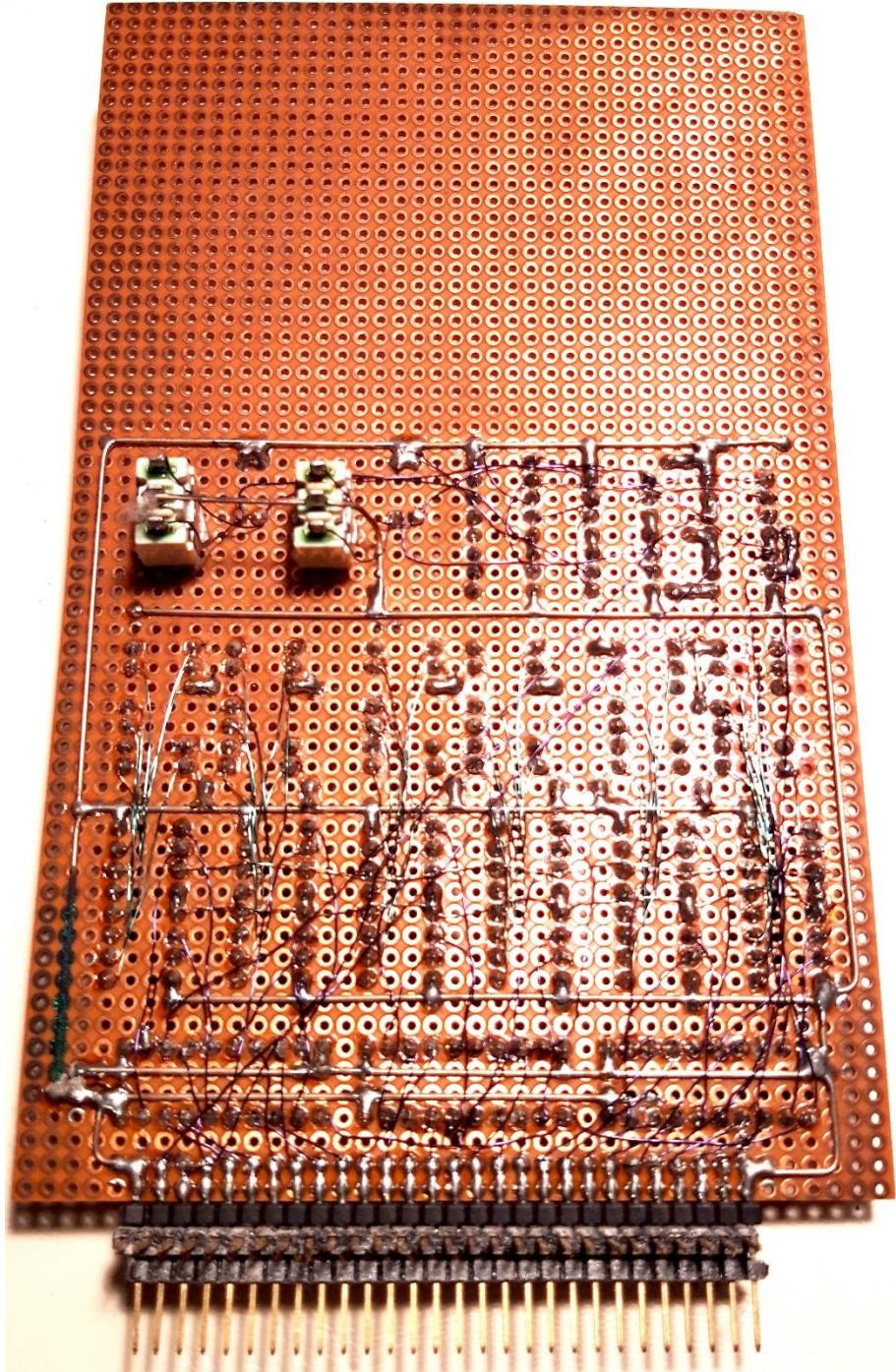

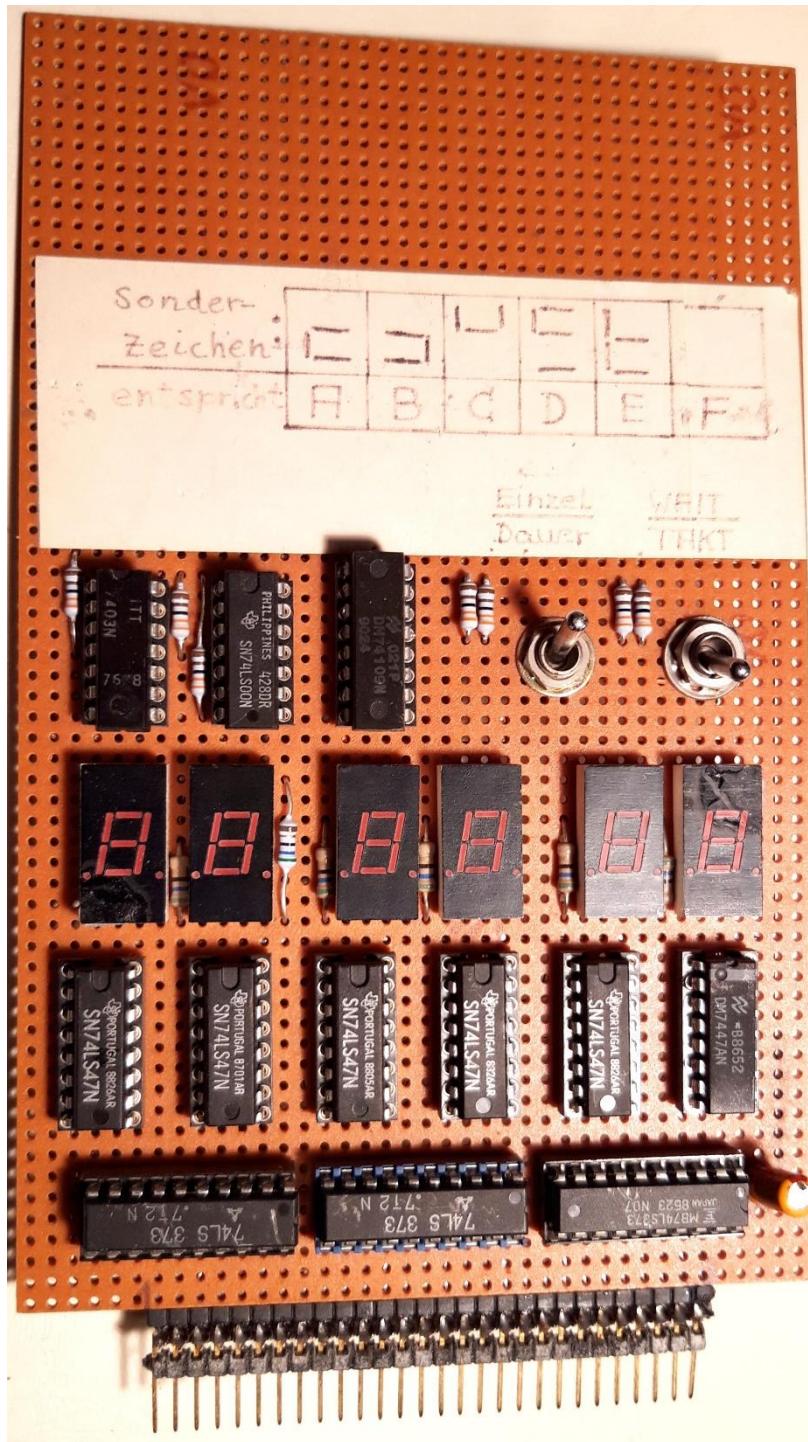

# Address Monitor Debug Board – TOP Side

Wird auf die Pfostenleiste parallel zu den DRams aufgesteckt.

Über die Kippschalter kann Einzeltakt Bearbeitung zum Debugging

Des Bootstrap Codes erreicht werden (ab Adresse 0x0).

# Address Monitor Debug-Board – Bottom Side